## High mobility $InGaZnO_4$ thin-film transistors on paper

Cite as: Appl. Phys. Lett. **94**, 072103 (2009); https://doi.org/10.1063/1.3086394 Submitted: 20 December 2008 . Accepted: 02 February 2009 . Published Online: 18 February 2009

Wantae Lim, E. A. Douglas, S.-H. Kim, D. P. Norton, S. J. Pearton, F. Ren, H. Shen, and W. H. Chang

## ARTICLES YOU MAY BE INTERESTED IN

High-mobility thin-film transistor with amorphous  ${\rm InGaZn}O_4$  channel fabricated by room temperature rf-magnetron sputtering

Applied Physics Letters 89, 112123 (2006); https://doi.org/10.1063/1.2353811

Low-voltage indium gallium zinc oxide thin film transistors on paper substrates Applied Physics Letters **96**, 053510 (2010); https://doi.org/10.1063/1.3309753

Origin of threshold voltage instability in indium-gallium-zinc oxide thin film transistors Applied Physics Letters **93**, 123508 (2008); https://doi.org/10.1063/1.2990657

## High mobility InGaZnO₄ thin-film transistors on paper

Wantae Lim, <sup>1</sup> E. A. Douglas, <sup>1</sup> S.-H. Kim, <sup>1</sup> D. P. Norton, <sup>1</sup> S. J. Pearton, <sup>1,a)</sup> F. Ren, <sup>2</sup> H. Shen, <sup>3</sup> and W. H. Chang <sup>3</sup>

(Received 20 December 2008; accepted 2 February 2009; published online 18 February 2009)

We report on the fabrication and the electrical properties of amorphous  $(\alpha\text{-})\text{InGaZnO}_4$  thin-film transistors deposited on cellulose paper by sputtering at room temperature. The 150- $\mu$ m-thick paper was used as both a gate dielectric and a substrate for device structural support. The transistors on paper were patterned by lithography and operated in enhancement mode with a threshold voltage of 3.75 V, and exhibited saturation mobility, subthreshold gate-voltage swing, and drain current on-to-off ratio of  $\sim$ 35 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, 2.4 V decade<sup>-1</sup>, and  $\sim$ 10<sup>4</sup>, respectively. These results verify that simple cellulose paper is a good gate dielectric as well as a low-cost substrate for flexible electronic devices such as paper-based displays. © 2009 American Institute of Physics.

[DOI: 10.1063/1.3086394]

Metal-oxide semiconductors (i.e., Zn-O, In-Zn-O and In-Ga-Zn-O) have been extensively investigated recently for optoelectronic applications, such as thin-film transistors (TFTs)<sup>1-3</sup> and light-emitting diodes,<sup>4</sup> due to their great potential for low-cost and large-area deposition. These recent reports have demonstrated that amorphous (α-)InGaZnO<sub>4</sub> films are good channel materials in TFTs fabricated on a variety of substrates, such as silicon, glass, polyimide, polyethylene terephthalate (PET), and polyethylene naphthalate, exhibiting high electron mobility and excellent surface smoothness. 5,6 Although  $\alpha$ -InGaZnO<sub>4</sub> (IGZO) films have several attractive features, a key issue for realization of highperformance flexible electronics is the choice of suitable gate dielectrics capable of being deposited at low temperature (<100 °C). In addition, commercial products targeting mechanical flexibility and low cost may require the use of cheap substrates. One approach to fulfilling these demands is to fabricate the device on regular paper as an alternative to polymeric substrates, because it is one of the most abundant materials and a recyclable resource. Some research groups have reported on organic transistors, organic TFT arrays, and polymer electrochromic displays using a paper substrate with a barrier layer coated in order to protect the substrate from water and solvent during processing. Fortunato et al. 10,11 have recently demonstrated the use of a cellulosefiber-based paper, which acts simultaneously as a substrate and a gate dielectric in oxide field-effect transistors. This approach is manufacturing-friendly and can be applied to various types of devices because of the simple fabrication process.

In this letter, we report the electrical properties  $\alpha$ -InGaZnO<sub>4</sub> TFTs fabricated on a cellulose paper at room temperature using a modified conventional lithography process. The suitability of the cellulose paper as a substrate and a gate dielectric in the transistor is also discussed.

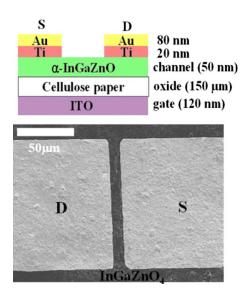

InGaZnO<sub>4</sub>-based TFTs were fabricated by rf-magnetron sputtering at room temperature using cellulose paper. The 150- $\mu$ m-thick cellulose paper was used as both a substrate

and gate dielectric in the TFT structure, as reported previously, <sup>10</sup> and as shown schematically in Fig. 1 (top). The device was constructed on both sides of the paper. To define the gate electrode, a 120-nm-thick ITO (In<sub>2</sub>O<sub>3</sub>-SnO<sub>2</sub>) film was first deposited by sputtering at room temperature on one side of the paper. The sheet resistance of ITO was  $\sim 100~\Omega^{-1}$ . Then, the IZGO channel layer with thickness of  $\sim$ 50 nm was deposited on the other side of the paper at room temperature using a 3 in. single target. For the channel layer deposition, the rf power and working pressure were 150 W and 10 mTorr in a mixed ambient of Ar/O<sub>2</sub>, respectively. The n-type carrier concentration in the film was  $\sim 10^{16}$  cm<sup>-3</sup>. Finally, sputtered Ti (20 nm)/Au (80 nm) source and drain electrodes were formed on the channel layer using a revised photolithography and lift-off process. Since the paper was found to deform on a macroscopic scale in developer solution, we reduced the developer exposure time to 15 s from our normal 45 s. This was found to be suitable for demonstrating functionality of the TFTs. A scanning elec-

FIG. 1. (Color online) Schematic of  $\alpha$ -InGaZnO thin film transistor (top) and SEM plan-view image of the device (bottom).

<sup>&</sup>lt;sup>1</sup>Department of Materials Science and Engineering, University of Florida, Gainesville, Florida 32611, USA <sup>2</sup>Department of Chemical Engineering, University of Florida, Gainesville, Florida 32611, USA

<sup>&</sup>lt;sup>3</sup>Sensors and Electron Devices Directorate, Army Research Laboratory, Adelphi, Maryland 20783, USA

a) Electronic mail: spear@mse.ufl.edu.

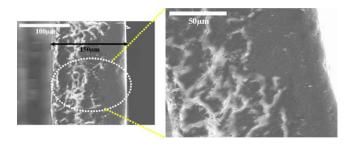

FIG. 2. Surface images of cellulose paper before and after channel deposition.

tron microscopy (SEM) plan-view image of the competed device is also shown in Fig. 1 (bottom). The channel length and length-to-width ratio were 6  $\mu$ m and 1:20, respectively.

To determine the dielectric constant of the cellulose paper, *C-V* measurements were performed at 1 MHz. For the metal-insulator-metal structure, Al was evaporated through a metallic shadow mask on both sides of the paper. The device dc-characterization was carried out in air at room temperature using an Agilent 4156C parameter analyzer.

The surface images of a cellulose paper before and after channel deposition are shown in Fig. 2. The InGaZnO<sub>4</sub> film deposited on the paper was somewhat rough to the eye, which is attributed to the relatively high surface roughness of the control paper. One of the most important factors for high-performance TFTs is the quality of the interface between the channel and gate dielectric. The existing surface morphology of the paper, acting as a gate dielectric in this study, obviously affects the interface roughness, suggesting that the device performance will be degraded due to a large interface trap density and high interface roughness between channel and gate dielectric. <sup>12</sup>

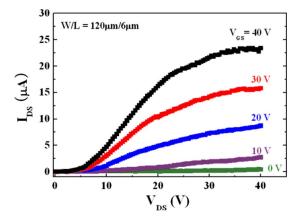

Figure 3 shows the typical output characteristics  $(V_{\rm DS}-I_{\rm DS})$  for  $\alpha$ -InGaZnO<sub>4</sub> TFTs with a 150- $\mu$ m-thick cellulose paper gate dielectric at different gate voltages  $(V_{\rm GS})$ . The channel length (L) and channel width (W) were six and 120  $\mu$ m, respectively. The transistors operated in enhancement mode with little drain current at zero gate voltage. A saturation current of 23  $\mu$ A was obtained at a  $V_{\rm GS}$ =40 V. Absorption of developer chemicals by the cellulose paper during the photolithography process leads to uneven surfaces due to the hydrophilic property of paper substrates. As a consequence, in the low drain voltage region, current-crowding behavior was observed, indicating a relatively high

FIG. 3. (Color online) The typical output characteristics of  $\alpha$ -InGaZnO<sub>4</sub> TFTs with a 150- $\mu$ m-thick paper gate dielectric.

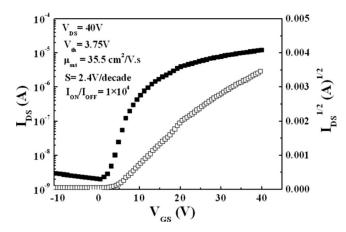

FIG. 4. The transfer characteristics of  $\alpha$ -InGaZnO<sub>4</sub> TFTs.  $V_{\rm GS}$  was swept from -10 to 40 V at a fixed  $V_{\rm DS}{=}40$  V.

resistance between the source and drain contacts. This is explained by the fact that the asperities of a paper substrate can deteriorate adhesion of metal electrodes to the channel layer, resulting in poor Ohmic contact on the channel layer. The corresponding transfer characteristics ( $V_{GS}$ - $I_{DS}$ ) for the device in the saturation region ( $V_{\rm DS}$ =40 V) are shown in Fig. 4. The device exhibited a low off current of  $\sim 10^{-9}$  A and drain current on-to-off ratio  $(I_{\rm ON}/I_{\rm OFF})$  of  $\sim 10^4$ . Fortunato et al. 10 suggested that the open structure of the cellulose paper can cause the severe degradation of off current in the transistor. While the cellulose paper used in this study has a relatively compact structure, as shown in Fig. 5, and the off current was improved by two orders of magnitude relative to devices reported previously on other cellulose papers, this is still in ratio with the size of the respective devices (the devices in Ref. 10 was much larger, having W/L=2165/216  $\mu$ m), i.e., the lower off current in our case comes from a smaller area, over which the device integrates the leaky dielectric.

Note that the subthreshold gate-voltage swing (S) for the paper-based TFT was relatively high (S=2.4 V decade<sup>-1</sup>), indicating that there was considerable carrier scattering by trapped charges at the InGaZnO<sub>4</sub>/paper interface. The high value of S may have resulted from both the poor Ohmic contact and rough surface of the paper as discussed above. The saturation mobility ( $\mu_{\rm sat}$ ) and threshold voltage ( $V_{\rm TH}$ ) were estimated from the slope and x-axis intercept of  $V_{\rm GS}$ -( $I_{\rm DS}$ )<sup>0.5</sup> curve using the standard saturation current equation. The  $\mu_{\rm sat}$  and  $V_{\rm TH}$  were 35 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and 3.75 V, respectively, where the capacitance per unit area was 40.48 pF cm<sup>-2</sup>. The corresponding effective dielectric constant ( $k_{\rm eff}$ ) of the paper was  $\sim$ 6.8. All device parameters

FIG. 5. (Color online) SEM cross-section images of cellulose paper with thickness of 150  $\,\mu m$ .

obtained here were comparable to those of InGaZnO<sub>4</sub> TFTs fabricated previously on glass or flexible substrates (PET or polyimide).<sup>5,13</sup> Although there is still problems with chemical absorption during wet process steps such as lithography, cellulose paper appears to be a promising candidate as a gate dielectric for low-cost flexible electronic applications. There are of course, many issues to address in future work, including the stability and robustness of the transistors. The use of different paper thickness or type will help reduce the voltage needed for gate control of the channel and deposition of a more highly doped IGZO contact regions will reduce contact resistance.

In conclusion, we have examined the electrical characteristics of  $\alpha$ -InGaZnO<sub>4</sub> TFTs fabricated using lithographic patterning on a cellulose paper at room temperature. The transistor showed low threshold voltage (3.75 V) and high saturation mobility ( $\sim$ 35 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>).

The work at UF was supported in part by the Army Research Office under Grant No. DAAD19-01-1-0603 (monitored by Dr. M. Gerhold) and the Army Research Laboratory and NSF (Grant No. DMR 0700416, Dr. L. Hess). We thank UFNF staff for their help in the performance of this work.

- <sup>1</sup>R. B. M. Cross, M. M. De Souza, S. C. Deane, and N. D. Young, IEEE Trans. Electron Devices **55**, 1109 (2008).

- <sup>2</sup>J. Y. Kwon, K. S. Son, J. S. Jung, T. S. Kim, M. K. Ryu, K. B. Park, B. W. Yoo, J. W. Kim, Y. G. Lee, K. C. Park, S. Y. Lee, and J. M. Kim, IEEE Electron Device Lett. **29**, 1309 (2008).

- <sup>3</sup>K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, Nature (London) **432**, 488 (2004).

- <sup>4</sup>H. K. Kim, K. S. Lee, and J. H. Kwon, Appl. Phys. Lett. **88**, 012103 (2006).

- <sup>5</sup>W. Lim, J. H. Jang, S. H. Kim, D. P. Norton, V. Craciun, S. J. Pearton, F. Ren, and H. Shen, Appl. Phys. Lett. **93**, 082102 (2008).

- <sup>6</sup>D. H. Kim, N. G. Cho, H. G. Kim, H. S. Kim, J. M. Hong, and I. D. Kim, Appl. Phys. Lett. **93**, 032901 (2008).

- <sup>7</sup>F. Eder, H. Klauk, M. Halik, U. Zschieschang, G. Schmid, and C. Dehm, Appl. Phys. Lett. **84**, 2673 (2004).

- <sup>8</sup>Y. H. Kim, D. G. Moon, and J. I. Han, IEEE Electron Device Lett. **25**, 702 (2004).

- <sup>9</sup>P. Andersson, D. Nilsson, P. O. Svensson, M. Chen, A. Malmstrom, T. Remonen, T. Kugler, and M. Berggren, Adv. Mater. (Weinheim, Ger.) 14, 1460 (2002).

- <sup>10</sup>E. Fortunato, N. Correia, P. Barquinha, L. Pereira, G. Goncalves, and R. Martins, IEEE Electron Device Lett. 29, 988 (2008).

- <sup>11</sup>R. Martins, P. Barquinha, L. Pereira, N. Correia, G. Goncalves, I. Ferreira, and E. Fortunato, Appl. Phys. Lett. **93**, 203501 (2008).

- <sup>12</sup>M. M. De Souza, S. Jejurikar, and K. P. Adhi, Appl. Phys. Lett. **92**, 093509 (2008).

- <sup>13</sup>W. Lim, S. H. Kim, Y. L. Wang, J. W. Lee, D. P. Norton, S. J. Pearton, F. Ren, and I. I. Kravchenko, J. Vac. Sci. Technol. B 26, 959 (2008).